# Computeranwendung in der Chemie Informatik für Chemiker(innen)

#### 2. Hardware

WS2003-04

## Grundlagen

Jede Computeranwendung besteht aus:

EingabeE

Verarbeitung

V

Ausgabe

Trennung oftmals aufgeweicht: Interaktive Programmausführung

## Grundlagen

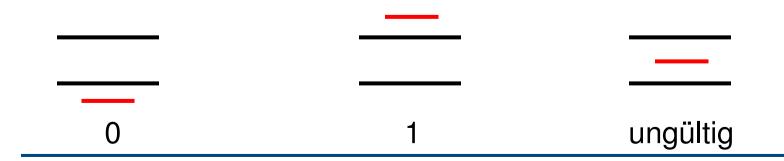

Computer: Rechenmaschine auf binärer Basis

⇒ "digital computer"

Informationen werden im binären System (nur 0 oder 1) darstellt.

Einfache Implementierung in Schaltkreisen über Spannungspegel/Schwellenwerte

## Grundlagen

Operationen im binären System:

Bool'sche Algebra

Grundoperationen: & (und/and), | (oder/or), ! (nicht/not)

$$0 & 0 = 0$$

$$0 \mid 0 = 0$$

$$!0 = 1$$

$$0 \& 1 = 0$$

$$!1 = 0$$

$$1 \& 0 = 0$$

$$1 \mid 0 = 1$$

$$1 \& 1 = 1$$

## Darstellung von Informationen

- Kleinste Informationseinheit: Bit (0 oder 1)

- Bit: Kunstwort aus Binary digIT ("Binäre Ziffer")

- 8 Bit = 1 Byte (2<sup>8</sup> = 256 verschiedene Werte)

- Word: normalerweise 16 Bit (65.536 Werte)

- Double word (dword): 32 Bit (4.294.967.296 Werte)

## Darstellung von Zeichen

|      | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0000 | NUL | DLE |     | 0   | @   | Р   | 6   | р   |

| 0001 | SOH | DC1 |     | 1   | Α   | Q   | а   | q   |

| 0010 | STX | DC2 | "   | 2   | В   | R   | b   | r   |

| 0011 | ETX | DC3 | #   | 3   | С   | S   | С   | S   |

| 0100 | EOT | DC4 | \$  | 4   | D   | Τ   | d   | t   |

| 0101 | ENQ | NAK | %   | 5   | Е   | U   | е   | u   |

| 0110 | ACK | SYN | &   | 6   | F   | V   | f   | V   |

| 0111 | BEL | ETB | •   | 7   | G   | W   | g   | W   |

| 1000 | BS  | CAN | (   | 8   | Ι   | Χ   | h   | X   |

| 1001 | H   | EM  | )   | 9   |     | Υ   | i   | У   |

| 1010 | LF  | SUB | *   | :   | J   | Z   | j   | Z   |

| 1011 | VT  | ESC | +   | •   | K   | [   | k   | {   |

| 1100 | FF  | FS  | ,   | <   | L   | \   | I   |     |

| 1101 | CR  | GS  | -   | =   | М   |     | m   | }   |

| 1110 | S0  | RS  |     | ^   | Ν   | ~   | n   | ٨   |

| 1111 | S1  | US  | /   | ?   | 0   | _   | 0   | DEL |

ASCII: American Standard Code for Information Interchange

## Darstellung von ganzen Zahlen

Ganze Zahlen (integer numbers)

- Darstellung als Binärzahl

- z. B. 32 bit Integer: 0 4.294.967.295

- Vorzeichenbehaftet (signed)

- höchstwertiges Bit als Vorzeichen (genau: Zweierkomplement)

- z. B. 32 bit: -2.147.483.648 2.147.483.647

## Darstellung von ganzen Zahlen

Beispiel: 5086 als 16 bit Integer:

$$5086_{10} = 0001001111011110_{2}$$

-5086 als 16 bit Integer:

$$-5086_{10} = 1110110000100010_2$$

Zweierkomplement: Alle Bits invertieren und 1 addieren

Überlauf gefährlich, da aus großen positiven Zahlen große negative Zahlen werden

$$32767_{10} = 01111111111111111111$$

$$-32768_{10} = 1000000000000000$$

#### Darstellung von reelen Zahlen

- Fließkommazahlen (floating point numbers)

- Getrennte Speicherung von Mantisse (kleine Festkommazahl) und Exponent

- Beispiel: "double precision" 64 bit

- 1 bit Vorzeichen

- 11 bit Exponent

- 52 bit Mantisse

- Darstellungsbereich: 2,23\*10<sup>-308</sup> 1,79\*10<sup>308</sup>

- Begrenzte Genauigkeit (64 bit: ca. 16 Stellen)

#### Maschinenbefehle

- Maschinenbefehle direkt von CPU ausführbar

- Jeder CPU-Type hat eigene Befehle (ISA: Instruction set architecture, z. B. IA32)

- Maschinencode nicht portabel

- Register: Speicherzellen innerhalb der CPU für Speicherung von Daten

- Begrenzte Anzahl

- sehr schnell

- Maschinenbefehle beziehen sich normalerweise auf Register

#### Maschinenbefehle

#### Beispiele für Maschinenbefehle:

- load/store (Transfer von Daten zwischen Hauptspeicher und Registern)

- add/sub/mul/div (Grundrechenarten)

- jump (Sprung an eine andere Adresse)

- compare (Vergleich von Werten)

- branch (bedingter Sprung, abhängig von vorherigem Befehl, z.B. für Verzweigung, Schleifen, etc.)

## Hauptspeicher

- flüchtiger Speicher (Daten bleiben nur bei Stromversorgung gespeichert)

- RAM: random access memory

- Problem: Fortschritt bei RAM-Geschwindigkeit kleiner als bei CPU-Geschwindigkeit

- Lösung: Cache (Zwischenspeicher), schneller als RAM, heute normalerweise in CPU integriert

- Verschiedene Cache-Stufen (1<sup>st</sup> level, 2<sup>nd</sup> level, etc.)

## Pipeline Konzept

Verarbeitung von Maschinenbefehl in einem CPU Takt nicht möglich.

- Pipeline: Zerlegung in kleinere Schritte (z.B. fetch, decode, execute, return), "Fließband"

- Mit jedem Takt wird ein Schritt ausgeführt

Problem: Unvorhergesehene Verzweigungen führen zum Verwerfen der Pipeline

Lösung: Sprungvorhersage (branch prediction)

AMD Athlon: 11 Stufen Pipeline

Intel P4: 20 Stufen Pipeline

WS2003-04

#### Schematischer Aufbau von PIII

**Instruction Cache**

Instruction Streaming Buffer

Instruction Length Decoder

**Decoder Alignment Stage**

Decoded 0 (complex)

Decoded 2 (simple)

Decoded 1 (simple)

Decode

**Fetch**

**Decoded Instruction Queue**

Register allocation

Reorder buffer

Execute

Store Data Store Addr. Unit

Load Addr. Unit Int. ALU ADD Move FPU AGU MUL/DIV Move ALU: Arithmetic and logical unit

AGU: Adress generation unit

Return

Data Cache

WS2003-04

# Speicherhierarchie

| Größe                  | Тур            | Latenz (Verzögerung)   |  |  |  |

|------------------------|----------------|------------------------|--|--|--|

| 8-128 *                | Register       | 0 ns                   |  |  |  |

| 32-128 Bit             |                |                        |  |  |  |

| 16-64 KByte            | L1 Cache       | 1-3 ns (2-3 Takte)     |  |  |  |

| 256-1024 KB            | L2 Cache       | 5-10 ns (ca. 10 Takte) |  |  |  |

| 100 MB – 4 GB <b>F</b> | RAM            | 20-40 ns (> 20 Takte)  |  |  |  |

| 20 – 200 GB            | virt. Speicher | > 1 ms                 |  |  |  |

|                        | (Festplatte)   |                        |  |  |  |

#### Parallel Architekturen

- Cluster

- Unabhängige Computer

- über Netzwerk verbunden

- "Shared memory"

- Mehrere CPU, die auf gemeinsamen Speicher zugreifen

- Vektor CPU

- Eine Instruktion verarbeitet Daten in mehreren Registern (SIMD: single instruction, multiple data)

- Implementierung in PC: MMX, SSE